'Tiny Bubbles' Could Empower IBM's Next-gen Power6 CPU

Of course, we're talking about the introduction of holes into the substrate of the chip. Wouldn't that reduce the structural integrity of the chip? "We are weakening it somewhat," IBM's Dan Edelstein admitted, "but not nearly as much. We're taking a stronger initial material, we're leaving it behind in many places where it matters for physical strength, and removing it where it matters for capacitance. As it turns out - we've proved this both by modeling and also by stress measurements - the impact of the overall chip mechanical strength is almost negligible, whereas the impact to capacitance is huge.

"The same goes for thermal conductivity," he added, "which is something we worry about. The insulator has to conduct heat from the wires down to the silicon to get rid of it. You would think that cutting slots in there would really degrade that, but in fact physically, the way the heat flows, the fact that we leave enough insulator behind is a good enough path that we barely see an impact."

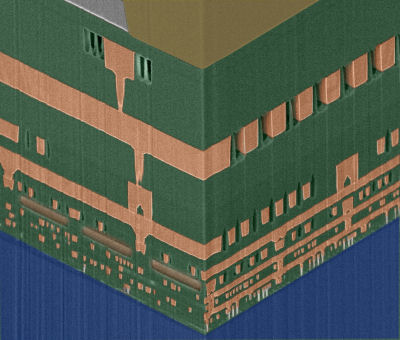

Keep in mind that IBM's fabrication tools aren't going into each chip and etching little holes one-by-one - an impossible task. Instead, at the smallest available wiring level, the most incredible part of IBM's process is that the holes are etched automatically, precisely where they need to be - a kind of self-alignment that IBM is explaining with the term "self-assembly." This is perhaps the most misunderstood part of the IBM process - what has led news sources everywhere to tout "chips that assemble themselves," which is hardly the case.

In reality, the etching process is configured so that for each successive layer, the copper doesn't get etched but the insulator surrounding the copper does. "There's some effect of self-alignment that goes on because the insulator etches and the copper doesn't," said Edelstein. "So when you're done, it looks like the gaps were aligned with the space between the lines, the wires."

The standard size of a gap, we're told, is about 20 nm, and will be adjustable as IBM's own fabrication process shrinks from 65 nm down to 32 nm. Edelstein declined to reveal specifics about how that scaling process happens, though he stated IBM already has a recipe in mind, which involves the synthesis of different molecules whose alignment allows for smaller airgaps.

The standard size of a gap, we're told, is about 20 nm, and will be adjustable as IBM's own fabrication process shrinks from 65 nm down to 32 nm. Edelstein declined to reveal specifics about how that scaling process happens, though he stated IBM already has a recipe in mind, which involves the synthesis of different molecules whose alignment allows for smaller airgaps.

The retooling investment for IBM's fabrication facilities could be zero, Edelstein tells us - in fact, that's one of the process' major selling points, as IBM most likely prepares to license it to other manufacturers.

But you can't just make the same chips faster by adding tiny holes...or at least, so it seems. If signaling speeds increase, and chip processing speeds increase in turn, as a result of implementing the airgap method, you'd think all the critical timing that's part of microprocessing would have to be tweaked.

So does this mean chips like the next-generation Power6 and Cell BE would need to be redesigned? As Edelstein told us, most high-performance microprocessors are CMOS chips, which are static by design and thus unlikely for their designs to be impacted by a speed boost. "On the other hand, you'll definitely get a power benefit, even without changing that circuit too much, because you decrease the load," he added. "Other processors might be highly timing-sensitive, and yes, you may have to retune them. The good thing is that, re-tuning, so to speak, or re-customizing some of these critical circuits can often be done with only maybe a redesign of one mask level."

But major CPUs might be able to take greater advantage of higher speeds, for example, by shaving some of their calls to the L2 cache, perhaps reducing the number of clock cycles required for some instructions. "There are different degrees of benefit one could attain," Edelstein said, "and it would depend on which processor."

IBM's test fabrication facilities have already been retooled, Edelstein told us, so the work that remains is for the team to test for likely yield and defect densities. "We don't have that much data," he remarked, "but what we do have looks quite clean."

The company's current round of Power6 processors will enable an 8P server to attain slightly better performance, according to TPCC benchmarks, than some 16P servers using IBM's previous generation. The airgap manufacturing method holds the promise of boosting IBM server performance by the same amount yet again, with the result being that the Power processor may extend its performance lead in the high-end segment over Intel's Itanium for at least two more years, if not longer.